芯片爆破测试是一种常用的安全评估方法,用于检测芯片中存在的潜在漏洞。然而,这种测试也有一些限制和局限性需要我们注意。在本文中,我们将介绍芯片爆破测试的几个主要限制,并探讨如何克服这些限制来提高测试的效果。

芯片爆破测试通常需要物理访问目标芯片。然而,在实际应用中,有时无法获得足够的访问权限来进行测试。比如,某些芯片可能被用于高度敏感的应用,对外界的物理接触有严格的限制。一些芯片可能已经安装在密封的外壳中,无法直接进行访问。

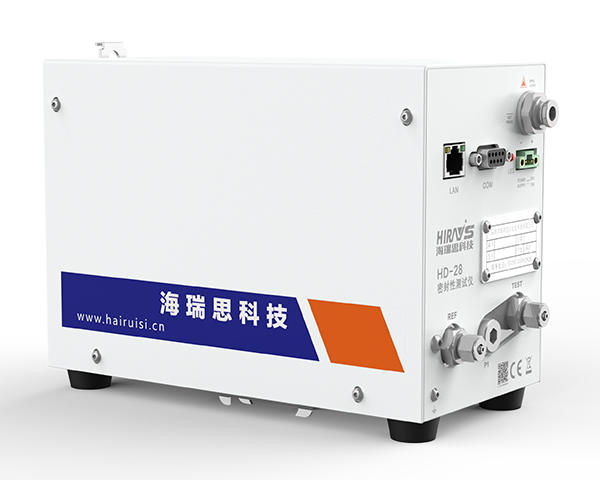

芯片爆破测试通常需要大量的资源和时间来完成。对于复杂的芯片,测试可能需要使用专门的硬件设备和软件工具。由于芯片上的电路复杂性和规模,测试可能需要花费数天甚至数周的时间来完成。对于一些项目来说,这样的资源和时间成本可能是难以承受的。

由于芯片的复杂性和多样性,芯片爆破测试通常无法实现对所有可能的攻击路径和漏洞的完全覆盖。即使使用了的测试工具和技术,也难以保证测试能够找到所有的漏洞。因此,测试人员需要根据风险评估的结果,选择有限的测试路径来进行测试。

芯片爆破测试面临着隐蔽性的挑战。由于芯片通常是应用于物理设备中的一部分,攻击者对于芯片的物理访问可能是非常困难和昂贵的。芯片上的攻击可能不容易被检测到,因为攻击者可以使用各种方法来隐藏其行为。

芯片爆破测试可以发现潜在的安全漏洞,但是验证这些漏洞的存在性和影响是一个挑战。由于测试通常是在控制环境中进行的,与实际的攻击场景可能存在差异。因此,需要进行额外的测试和验证,以确认这些漏洞的存在性和对系统安全的影响。

芯片爆破测试是一种重要的安全评估方法,但也有其局限性。我们需要认识到这些限制,并采取相应的策略和方法来克服它们。通过合理规划测试的范围和时间,与合适的专业人员合作,并加强对安全漏洞的验证,我们可以提高测试的效果和可靠性,从而更好地保护芯片的安全性。